迎接現今生成式AI驅動半導體產業變局,台灣該如何在護國神山的基礎上,強化次世代功率半導體和面板級先進封裝的供應鏈韌性與生態系尤為關鍵。

因應目前GPU尺寸越做越大,又要能封裝進入邏輯、射頻等愈來愈多且複雜的晶片。根據摩根士丹利最新報告,若以NVIDIA的H200 GPU為計算基礎,單片12吋晶圓約可封裝29組H200 GPU,但到了B200則僅能封裝16組。

因此繼CoWoS後,台積電再以「化圓為方」的CoPoS(Chip-on-Panel-on-Substrate)封裝IC技術成為市場焦點。

透過該技術直接於大型方形面板基板上排列晶片,即相當於捨棄傳統圓形的12吋晶圓的7倍之多,將大幅提升產能與面積利用率,可增加產出效益並有效降低成本。「同樣單位面積能放更多晶片,單位封裝成本就能降低」且CoPoS封裝結構上也會更具彈性,適合多樣化晶片尺寸與應用需求,未來有望進一步整合矽光子CPO等技術。

預計2026年將落腳台積電旗下采鈺科技公司,設立首條CoPoS實驗線;並敲定在嘉義AP 7廠引進設備生產,預計於2028 ~2029年間實現大規模量產,主要鎖定客戶端推動AI基礎建設帶動下的邊緣運算、ASIC(特殊應用積體電路)、5G與HPC高效能運算等高階應用。

晶圓、面板龍頭定規格 封測、設備廠跟進

且隨著面板級封裝趨勢逐漸成形,早已吸引國內外封裝大廠投入多年,包括日月光、力成等,選定的尺寸也各自不同。甚至傳出扇出型面板級封裝(FOPLP)可望接棒CoWoS,成為未來AI晶片封裝新主流,包含晶圓代工龍頭台積電、日月光、力成、群創、SpaceX等,主要就是看好FOPLP能增加大尺寸AI晶片產量並降低成本。

| 圖一 : 繼CoWoS後,台積電再以「化圓為方」的CoPoS封裝IC技術成為市場焦點。(攝影:陳念舜) |

|

晶圓代工大廠台積電也在今年傳出面板級封裝尺寸(Panel Level Packaging;PLP),將制訂在310 x 310mm尺寸的方形基板,帶動相關設備廠全力投入開發該尺寸設備。日月光則除了利用旗下矽品分食輝達CoWoS-S訂單,還有正積極跨入開發「系統式扇形封裝」產品。

包括首座「面板級扇出型封裝」(FOPLP)量產線落地高雄廠,也就是把晶片擺放的圓形晶圓(wafer)基板,變成「方形」面板基板600x600mm規格。並認為這會是未來扇出型面板級封裝(FOPLP)的主流規格,最早規劃沿襲的尺寸是300x300mm的方形基板。

當年底小批量生產尺寸開始調整為310x310mm,被外界認為是跟隨台積電的CoPoS規格,或將成未來業界面板級封裝尺寸主流,預定2026年可開始陸續送樣給客戶完成認證,隨後將正式量產出貨。

然而,前有CoWoS經歷了10年的醞釀,才隨著AI起風高飛,這次設備業者同樣又問起「客戶在哪?」的疑慮。事實上,因面板級封裝層次不同,不只台積、日月光,面板廠起家的群創,以及10年前就投入的力成,甚至早在2016年就建置面板級封裝產線。

只是當時主要用在封裝射頻IC或電源IC,技術上不是問題。而是跨入扇形2D先進封裝,再到台積現在異質整合的2.5D堆疊式封裝,技術等級不同,進攻的客戶便鎖定AI伺服器用的大尺寸高階運算晶片。

目前面板級封裝(PLP)憑藉「化圓為方」的先天優勢,在成本效益方面具備競爭力,據傳輝達、AMD都在思考面板級封裝的可能,延續台積電現正當紅的晶圓級CoWoS技術,可望成為未來AI晶片先進封裝新主流,確實帶動既有半導體後端製程封測、自動化設備產業鏈升級。

兩岸面板延長賽 再戰半導體封裝

就連中國大陸面板龍頭京東方,也傳出正推進半導體玻璃基板業務,向自動光學檢測(AOI)、無電解銅鍍等所需設備供應商發出採購訂單,試圖以顯示器中累積的玻璃基板技術為基礎,將業務擴展到半導體領域。

根據京東方公布2024~2032年技術路線圖,制定了清晰的玻璃基板技術演進路徑:2027年實現深寬比20:1,細微間距8/8μm,封裝尺寸110x110mm的量產能力;2029年進一步提升至5/5μm以內、封裝尺寸120x120mm以上。

迎合面板級先進封裝需求 TGV技術為關鍵

隨著高速運算、高頻通訊、AI加速器及高效能伺服器等應用快速推進,為因應小晶片與AI客製化晶片等新世代先進封裝需求,利用面板級封裝(Panel-Level Packaging;PLP)的大面積、低成本與高效能優勢,使玻璃穿孔(Through Glass Via;TGV)技術成為先進封裝關鍵工藝。

必須具備低介電常數、優異熱穩定性及高密度I/O整合能力,應用於玻璃芯(Glass Core)與2.5D/3D中介層(Interposer)等高階封裝結構。但在改變不同高低價位的玻璃材質時,TGV前段製程中的雷射改質品質長期無法即時掌握,成為良率與成本控制的挑戰。

因此由工研院成功開發全球首創「面板級封裝高深寬比全濕式完整解決方案」,達到材料、設備全國產化。結合全濕式面板級封裝設備,已突破TGV高深寬比製程的限制,成功將12吋填孔深寬比從AR 10提升至AR 15,提升封裝效率與密度達5成以上;同時運用高速掃描雷射與蝕刻技術,使鑽孔速度提升10倍,並確保百萬孔缺陷率低於1%,良率高達99%以上,大幅降低成本。

更以全濕式金屬化填孔取代PVD傳統乾式鍍膜,並提供完整鑽孔、填銅、研磨與檢測等解決方案,有效提高封裝密度與導通效率,使生產成本節省50%。

| 圖二 : 由工研院成功開發全球首創「面板級封裝高深寬比全濕式完整解決方案」(攝影:陳念舜) |

|

目前已整合設備廠、材料廠、元件廠,包括:聯策、誠霸、超特、立誠、旭宇騰等成立面板級封裝技術研發聯盟與產業鏈,為台灣設備與材料業者創造新一波合作契機。未來甚至可支援異質整合封裝,應用於高頻高速傳輸之通訊晶片、運算晶片上,提升台灣封裝產業的全球競爭力。

另有半導體封裝測試解決方案廠蔚華科技,推出業界首創「蔚華雷射斷層掃描(SpiroxLTS)」技術,結合多項專利非線性光學組合技術,透過非破壞性、零接觸、零損傷地直接觀測TGV玻璃內雷射改質斷層圖,解決TGV改質無法被看到的問題,將有助於TGV業者加速量產時程,獲得業界指標性雷射改質設備商海納光電、Glass Core製造商晶呈科技,以及TGV玻璃基板技術領導廠商欣興電子肯定。

目前SpiroxLTS已優先導入Glass Core與Interposer等高頻高速封裝應用,支援材料評估、製程導入與量產監控,將成為TGV工藝量產的重要推動力。

國儀中心攜手鼎極科技 雷射研磨碳化矽增產能

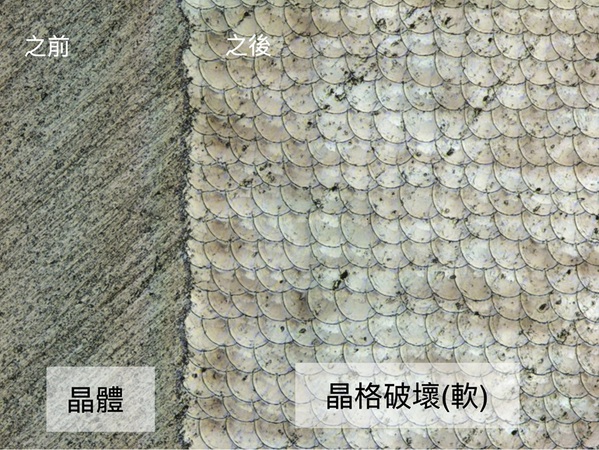

隨著電動車、AI算力乃至綠電等發展,半導體主要材料從較軟的矽提升到硬度僅次鑽石的「碳化矽」,導致製造成本大幅上升,晶圓破片率也達5~10%。惟透過國研院國儀中心與鼎極科技攜手合作,共同開發「紅外線奈秒雷射應用於碳化矽(SiC)晶圓研磨製程」的關鍵技術。

| 圖三 : 在共焦光學顯微鏡下,顯示SiC加工前後對比照。(source:國儀中心) |

|

可將每片晶圓的研磨時間從3小時縮短為2小時,且不會造成晶圓損傷,晶圓破片率可自5%降至1%,大幅提高產品良率。再由鼎極科技已與美國晶片製造商安森美半導體公司(ON Semiconductor Corp.)捷克廠合作,將機台推廣到歐洲,未來潛力無窮。