簡介

- 3D NAND快閃記憶體的產品目前配有超過300層堆疊氧化層和字元線層,以滿足位元儲存能力方面的需求。

- 記憶體產業持續增加如此驚人的堆疊層數,但是必須採用附加的「微縮加速器」才能實現這點。

- 其中一種微縮加速器是垂直間距(z-pitch)微縮,這項技術與降低氧化層/字元線層的厚度有關,藉此就能以可控的成本堆疊更多的元件層。

- imec正在開發兩項可在不犧牲記憶體運作和可靠度的情況下實現垂直間距微縮的關鍵技術:氣隙整合與電荷捕捉層分離。

LNAND快閃記憶體:業界主要的儲存技術

NAND快閃記憶體(NAND Flash)自1980年代晚期引進記憶體市場,持續不斷推動我們存取大量資料方式的革命性變革。這項熱門的記憶體技術在架構上鎖定高密度資料儲存進行優化,可見於所有主要的終端電子裝置市場,包含智慧手機、資料伺服器和個人電腦。你也能在SD記憶卡和UCB隨身碟等最方便拆卸與可攜式的記憶體裝置內發現這項技術。

這種記憶體具備非揮發性,能夠存取照片、影片、音檔、封存電子信件及其他元件長達十年。最近,NAND快閃記憶體技術也在人工智慧(AI)和機器學習(ML)扮演重要角色。例如,透過提供有效率的儲存設備來滿足訓練AI模型所需的大量資料。

NAND快閃儲存技術的成功歸功於持續擴增儲存密度及縮減成本的能力。NAND快閃記憶體產業每年會大幅改良位元儲存密度,這點體現在增加Gbit/mm2。為了持續朝這個方向發展,幾項技術創新不斷在推行。最重大的發展包含從2D到3D NAND快閃記憶體的發展動向、增加記憶體單元的儲存位元數(在商用NAND快閃記憶體最多4位元),以及從浮閘(floating gate)電晶體改用電荷捕捉(charge trap)單元來操作記憶體。

3D環繞閘極儲存結構:NAND快閃記憶體產業的生產主力

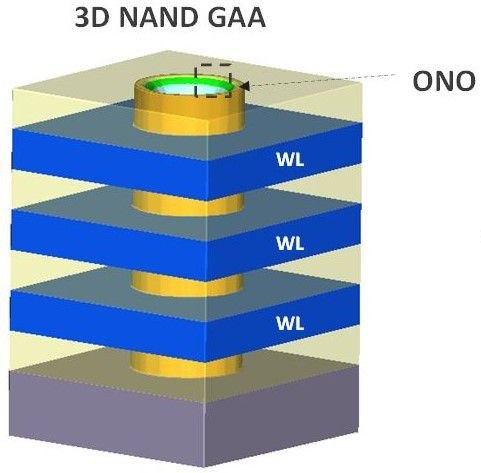

記憶體單元採用環繞閘極(GAA)垂直結構的3D NAND快閃記憶體是業界高密度資料儲存應用的生產主力。在這種3D結構中,記憶體單元相互堆疊,以形成一條垂直串列,而記憶體單元的定址則交由水平方向的字元線處理。

在多數的3D NAND產品中,電荷捕捉單元係作為儲存元件。這種記憶體單元就像是MOSFET電晶體在其閘極氧化層額外插入一層氮化矽(SiN)薄層。此舉將閘極氧化層變成氧化物/氮化物/氧化物(oxide-nitride-oxide)堆疊,或稱作ONO堆疊,這些元件層分別作為阻隔氧化層、捕捉氮化層與穿隧氧化層。

這層氮化矽包含多個能夠捕捉電荷的電荷捕捉位置。當閘極的電極呈現正偏壓,通道區域的電子會穿過氧化層,然後在氮化矽(SiN)層被捕捉。這會提高電晶體的臨界電壓。記憶體單元的儲存狀態可透過在源極/汲極之間施加電壓來測量。如果電流呈現流動狀態,這表示並未捕獲電子:記憶體單元處於「1」的狀態。若沒測到電流,記憶體單元則是處於「捕獲電子」或「0」的狀態。

| 圖一 : 3D NAND環繞閘極(GAA)結構顯示一串垂直方向的電荷捕捉記憶體單元,其中包含氧化物/氮化物/氧化物(ONO)閘極介電層與數量有限的字元線(WL)。 |

|

這種電荷捕捉單元採用一種環繞閘極垂直通道的方法來導入3D NAND結構。想像把平面電晶體結構翻轉超過90度角,包含此時被閘極堆疊包圍且呈現垂直方向的多晶矽傳導通道。

製造這種環繞閘極的第一步驟是成長出一個矽氧化層/字元線層的堆疊。接著,利用先進的乾式蝕刻工具來掘入該堆疊,形成圓柱型孔洞。隨後,沿著這些孔洞的側壁來沉積氧化層、捕捉層與多晶矽通道。這種配置通常稱作通心粉通道(macaroni channel)。

運用更多氧化層/字元線層來延續NAND快閃記憶體的發展藍圖

在未來幾年,記憶體產業將推動基於環繞閘極的NAND快閃記憶體發展,將其推向極限。目前,主要大廠提供配有超過300層氧化層和字元線層的3D NAND快閃記憶體產品,這些元件層相互堆疊。堆疊層數未來會再增加,預計在2030年前達到約1000層—相當於100Gbit/mm2。不過為了確保一條直徑一致的串列得以貫穿這層厚度約30微米(μm)的元件層堆疊,導致製造複雜度和成本增加,考驗著多層堆疊沉積和高深寬比蝕刻的製程步驟。

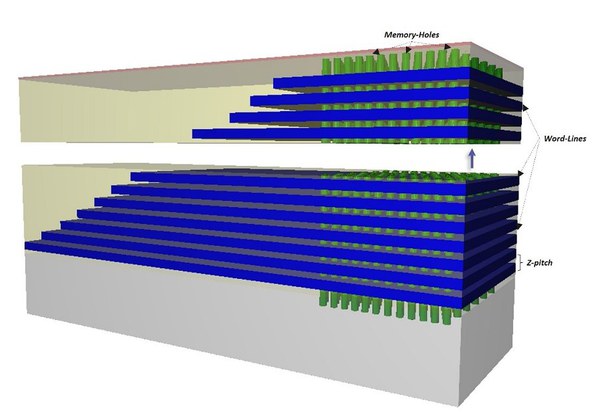

作為補助的「微縮加速器」因此添入工具箱。這些加速器包含增加每個記憶體單元的儲存位元數、縮短環繞閘極單元的x-y間距(橫向微縮)、提升記憶體陣列的面積效率,以及模組堆疊。另一項趨勢是在另一塊晶圓上面優化周邊的CMOS電路,再利用異質晶圓接合技術把這些電路連接到記憶體陣列堆疊。為了控制這些持續增長的製程成本,目前也在追求垂直方向的額外微縮,稱之為垂直間距(z-pitch)微縮。

| 圖二 : 3D NAND快閃記憶體環繞閘極(GAA)架構示意圖,另指出相鄰字元線之間的垂直間距(z軸間距)。 |

|

垂直間距微縮:優勢與隱患

為了持續降低新一代多層堆疊GAA NAND快閃記憶體的成本,3D NAND快閃記憶體的垂直間距微縮至關重要。採用垂直間距微縮,相鄰字元線之間的間距(目前大約是40奈米)得以進一步縮小,方法是同時微縮堆疊內部字元線和矽氧化層的厚度。如此一來就能在堆疊高度的每一微米增加更多的元件層,從而增加更多的記憶體單元,提供成本優勢。

不幸的是,從實驗中發現,在未經優化的情況下,垂直間距微縮會對記憶體單元的電氣性能產生負面影響,導致臨界電壓降低、次臨界擺幅(sub-threshold swing)增強、資料保留時間縮短,以及寫入和抹除電壓增加。

這些影響可歸因於兩種在持續微縮時越來越明顯的物理現象:記憶體單元之間的干擾與橫向電荷遷移。

當持續縮短字元線層的厚度時,電荷捕捉電晶體的閘極長度也隨之縮減。因此,閘極逐漸失去對通道的控制,導致相鄰的記憶體單元之間容易產生靜電耦合。除了記憶體單元之間的干擾現象,記憶體單元的垂直高度縮減也導致橫向電荷遷移(或垂直電荷損失):捕捉在氮化矽(SiN)層內的電荷容易透過垂直方向的氮化矽(SiN)層遷移,導致資料保留時間的損失。

接下來,我們探討有助於抑制這些現象的技術,讓研究人員為下世代3D NAND快閃記憶體解鎖垂直間距微縮。

整合字元線之間的氣隙來減少記憶體單元之間的干擾

科技電腦輔助設計(TCAD)的模擬顯示,在相鄰的字元線之間整合一條氣隙是抑制記憶體單元之間相互干擾的潛力方案。相較於閘極間距內的矽氧化物介電層,氣隙具備較低的介電常數,減少了相鄰記憶體單元之間的靜電耦合。這套「戲法」在較早開發的平面式2D NAND快閃記憶體結構中成效相當良好。然而,在多層的矽氧化物/字元線堆疊內導入氣隙顯然更加複雜。目前已經提出一些解決方案,但都尚未證實具備充分的可調能力。

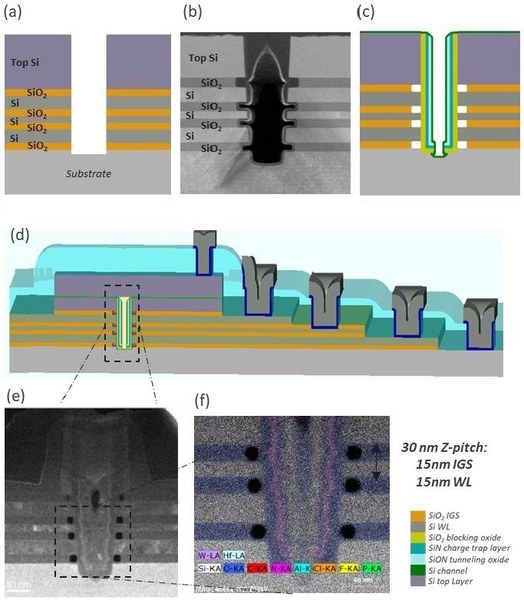

在2025年IEEE國際記憶體研討會(IMW)上,比利時微電子研究中心(imec)發表了一款獨特的整合方案,能透過可控的方式在字元線之間形成氣隙。這套整合方案包含從可用的記憶體區塊的內部區域導入氣隙,方法是在沉積氧化物/氮化物/氧化物(ONO)堆疊之前掘入閘極間距內的矽氧化層。氣隙以自對準的方式導入字元線,使其定位得以精準控制,並提供一套具備可調能力的解決方案。

| 圖三 : (a-d)氣隙的3D 整合製程流程;(e-f)上述製程所製出的氣隙之穿透電子顯微鏡(TEM)與能量色散X射線光譜儀(EDS)影像(發表於2025年IEEE國際記憶體研討會)。 |

|

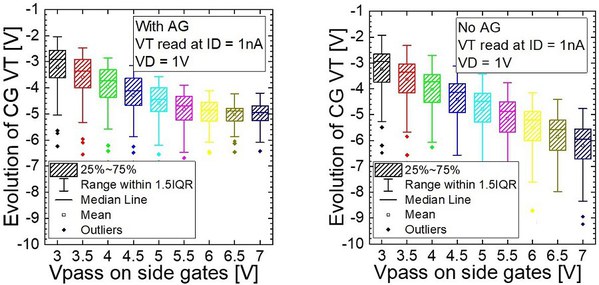

結果顯示,相較於不含氣隙的元件,包含單個氣隙的元件對相鄰記憶體單元的干擾較不敏感。這點是根據包含氣隙的元件在對非選取的閘極施加所謂的通行電壓(pass voltage)時所測得的臨界電壓變化較小而推斷。

這些結果是在一款測試元件上取得,該元件包含間距為30奈米(閘極長度為15奈米,閘極間距內的矽氧化物介電層為15奈米)的有限字元線層,而且可用記憶體區塊的直徑為80奈米。imec研究人員也在研究氣隙對記憶體性能和可靠度的影響。這些氣隙並未影響記憶體的運作,也顯示出多達1000次的重複寫入/抹除次數,與不含氣隙的元件相當。

| 圖四 : 在不同通行電壓(pass voltage)下,電荷捕捉元件的臨界電壓變化(左)包含氣隙,以及(右)不含氣隙(發表於2025年IEEE國際記憶體研討會)。 |

|

基於這些結果,記憶體區塊側的氣隙整合方案被視為用來積極微縮垂直間距的關鍵步驟。

引進電荷捕捉層分離來抑制橫向電荷遷移

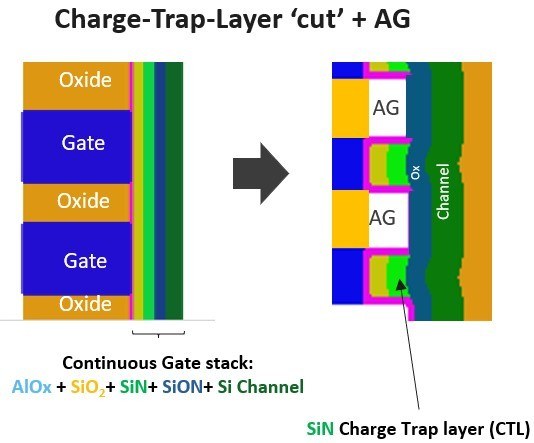

迄今,imec已經展示在閘極間距內的介電層導入氣隙的可行性,包含「終止」於氧化物/氮化物/氧化物(ONO)堆疊內的阻擋氧化層之氣隙。科技電腦輔助設計(TCAD)模擬顯示,把氣隙進一步延伸到阻擋氧化層和氮化矽(SiN)電荷捕捉層區域可能帶來更廣泛的電壓操作範圍。這種電荷捕捉層分離(或電荷捕捉切割)還有一項好處:這能避免捕捉在記憶單元的電荷穿過氮化矽(SiN)串列進行橫向遷移,該串列沿著氧化物/字元線堆疊的高度從上而下運行。

然而,導入這種電荷捕捉切割極具挑戰,因為需要穿過極深且極窄的記憶體區塊側壁進行定向蝕刻和沉積。可用來製造平面2D NAND快閃記憶體的技術工具箱已經不適用於這些結構。imec目前正與其供應商研究能以可控方式實現這種電荷捕捉切割的新技術。

一旦成功截斷電荷捕捉層,imec研究人員打算結合電荷捕捉切割與氣隙整合方案,為垂直間距微縮挑戰提供一套完整且可擴充的解決方案。

| 圖五 : (左)連續閘極堆疊示意圖,以及(右)包含整合式電荷捕捉層切割和氣隙整合方法的閘極堆疊示意圖。 |

|

結語與展望

為了控制字元線層持續增加所帶來的成本,基於環繞閘極的3D NAND快閃記憶體的垂直間距微縮是關鍵。imec基於其長久累積的製程專業和強大的設備供應商生態系統,正在開發用來支援垂直間距的積極微縮,同時維持記憶體運作和可靠度的關鍵技術:氣隙整合與電荷捕捉切割。

隨著配有環繞閘極電荷捕捉儲存結構的3D NAND快閃記憶體密度增長在未來達到飽和,世界各地的研究團隊也在探索更具破壞性的儲存結構來延續2030年以後的儲存技術藍圖。舉例來說,在近期提出的新型3D架構中,記憶體單元的傳導通道以水平方向設置,而非垂直方向。在另一套imec於2023年IEEE國際記憶體研討會探討的做法中,電荷捕捉記憶體單元透過溝槽型的結構來連接,而非利用環狀的環繞閘極(GAA)幾何圖形來整合記憶體單元—這能大幅提升位元儲存密度。

所有的這些技術開發顯示,目前有幾項開發中的技術未來將能讓記憶體產業逐步邁向超過100Gbit/mm2的資料儲存—主要由雲端運算和人工智慧(AI)應用所驅動的需求。

(本文由Imec提供,作者為imec記憶體製程整合團隊的整合技術資深研究員Sana Rachidi、imec儲存記憶體研究計畫主持人Maarten Rosmeulen)