開放式高速互連協定CXL記憶體介面的近期導入提供新興記憶體全新契機,在資料密集型運算應用中,與動態隨機存取記憶體(DRAM)各顯優勢。imec的研究顯示,包含氧化銦鎵鋅(IGZO)傳導通道的3D整合式電荷耦合元件(CCD)記憶體是絕佳的潛力元件。

AI與機器學習如何改變傳統的運算架構

| 圖一 : 透過技術發展可以提高DRAM密度,以解決對DRAM持續增長的需求,並跟進處理器邏輯元件的性能升級。 |

|

數十年來,動態隨機存取記憶體(DRAM)一直是傳統馮紐曼電腦架構的主要記憶體。其功能是暫時儲存資料和程式碼,並利用雙倍資料速率(DDR)匯流排,把這些資訊饋入處理器的快取記憶體。DRAM能以位元組(byte)為定址單位,這表示它可以一次定址單個或數個位元組。其中一個最關鍵的指標是短延遲,即在50奈秒的時程內完成第一個位元組定址的能力。快速擷取程式碼最需要這項規格,這些程式碼一般包含隨機分佈在DRAM晶片內的分支指令。

透過技術發展可以提高DRAM密度,以解決對DRAM持續增長的需求,並跟進處理器邏輯元件的性能升級。不幸的是,大約從2015年開始,DRAM的成本微縮—以每位元的單位成本表示,越來越難跟上摩爾定律。

與此同時,AI與機器學習等資料密集型應用也在改變馮紐曼電腦架構。為了執行針對特定應用的任務,現在有更多顆與更專用的處理器核心(圖形處理器、張量處理器等)同步運作。由於這些應用對於資料的需求極高,更大型的資料串(沒有太多程式碼)從記憶體傳送到這些處理器,提高了對DRAM記憶體的需求。目前正在引進新的內連導線標準來完善平行DDR匯流排的功能,以協助大量的資料傳輸。

開放式高速互連協定CXL就是其中之一,這是一套用於處理器和記憶體的開放式高頻寬內連標準,能更有效率使用DRAM記憶體。CXL支援多種應用案例,提供不同類型的標準,稱作第一類(Type 1)、第二類(Type 2)與第三類(Type 3)。最後一種也稱為Type 3緩衝記憶體,可望作為一種外接記憶體池,透過高頻寬CXL交換器來把大型資料區塊饋入多種處理器核心。

3D電荷耦合元件:CXL Type 3緩衝記憶體代替DRAM方案

儘管業界在研發搭配CXL介面的DRAM技術,imec採取不同的做法。imec研究團隊先是發現CXL記憶體—尤其是Type 3緩衝記憶體,可能擁有別於DRAM的特性。尤其是針對讀取第一個位元的延遲高要求—這也是很難改用另一種記憶體來取代DRAM的原因,在這些CXL Type 3結構中,可以放低這方面的標準。前提是新的記憶體技術能夠符合成本效益,並在極短時間內處理大型資料區塊,以補償讀取第一位元的延遲變長。

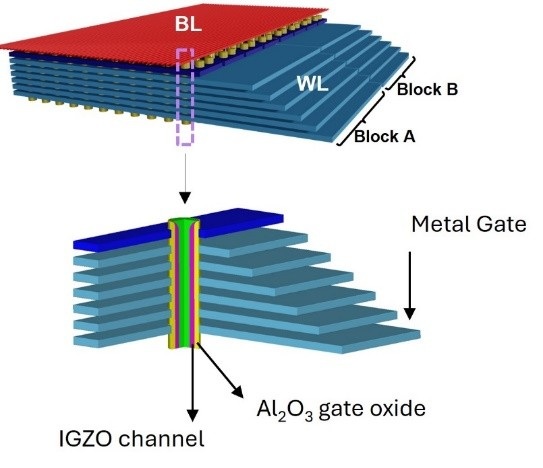

imec近期發表了一種新的記憶體概念,可望滿足CXL Type 3區塊可定址記憶體的所有需求:採用一種類似NAND記憶體的3D結構並搭配氧化銦鎵鋅(IGZO)通道的一款電荷耦合元件(CCD)。

在CCD元件內,要把資料寫入CCD暫存器,方法是把電荷載入由MOS電容器組成的不同階段,每個電容器都能儲存一位元的資訊。基本上,這是序列式運作,類似於人力接龍(bucket brigade)的傳輸方式:電荷饋入第一階段。接著傳到下一階段—每階段由數個相位閘極控制(通常是三個或四個)。該運動持續進行,直到第一個電荷傳送到能讀取資料的輸出端。把CCD用作記憶體元件的做法可以追溯到1970年,但很快就因為以位元組為定址單位的DRAM而顯得相形見絀。隨後,這項技術引入影像感測器市場,並在此進一步發展。因此,基礎的CCD技術廣為人知,也很可靠。加上以電荷為基礎,展現了功率效率。

imec概念的創新之處是其特定的3D特性,促使CCD技術具備超高的密度及成本效益。這套擬定的3D架構受到3D NAND技術的啟發,3D NAND的三個面向都有記憶體單元。在3D NAND結構內,這些記憶體單元相互堆疊,形成一條垂直串列,並由水平方向的字元線定址。製造採用一種「打孔填充(punch and plug)」的製程:先成長一層字元線堆疊,接著利用先進的蝕刻製程來穿鑿這層堆疊,形成圓柱型孔洞。隨後,包含一個多晶矽通道的NAND專用層沿著孔洞的側壁沉積。[2]

imec提出的3D CCD緩衝記憶體概念使用相似的方法:多顆CCD暫存器整合到垂直對齊的孔洞,每顆暫存器由一串MOS電容器單元組成。一項關鍵技術是利用氧化物半導體(例如氧化銦鎵鋅)通道材料,而非多晶矽。氧化銦鎵鋅(IGZO)可以透過原子層沉積(ALD)技術來沉積,在這樣高深寬比的結構內實現均勻一致的沉積。採用氧化銦鎵鋅的另一個好處是資料保留時間相對較長。如此就較不需要頻繁重新寫入記憶體,而這點是DRAM記憶體的一大缺點。

基於氧化銦鎵鋅的2D CCD概念驗證結構

為了導入實際應用,imec的第一步是在一套2D概念驗證展示這款包含氧化銦鎵鋅(IGZO)材料的CCD記憶體運作。這種平面式CCD結構包含1個輸入級、142個階段(每階段包含四相閘極,且可儲存1位元)以及1個基於雙電晶體的讀取級。為了把資料寫入CCD暫存器,要從輸入級注入電荷,接著依序經過142個階段來傳輸電荷—透過切換相位閘極的電壓來實現。

這款CCD元件提供超過200秒的資料保留時間、超過1010 次的重複讀寫次數,且未出現衰退,還有高於6MHz的電荷傳輸速度。該CCD暫存器的多階儲存能力也展現出能有助於提高位元密度。

高密度、低成本的3D氧化銦鎵鋅CCD緩衝記憶體

這套概念因為具備類似3D NAND的結構,所以製造的成本效益更甚於DRAM。但在位元密度方面,3D CCD緩衝記憶體也能打敗DRAM嗎?DRAM預計會在2030年達到1Gb/mm2的規格。為了回應這點,imec研究人員結合2D CCD概念驗證結構的特性及NAND快閃記憶體目前可達到的規格,估算了這款新型3D緩衝記憶體的位元密度。他們假設每記憶體單元為雙位元,陣列面積的使用損失率為30%,該損失率由字元線上的金屬接點配置決定。另採用了三相時脈運作。這表示每階段包含三種不同的相位,每階段的等效相位閘極接收相同的時脈訊號。

就NAND快閃記憶體目前所能實現的規格來說(至少230層的處理能力),imec預估,相較於(2D)DRAM預計在2030年前達到的規格,這種3D緩衝記憶體已經能提供5倍的位元密度。而3D NAND快閃記憶體的發展尚未止步:有些記憶體晶片製造商承諾會在2030年前製出1000層的產品。因此,就位元密度來說,區塊可定址的新型記憶體可望大幅領先DRAM。imec研究人員目前著手利用有限的字元線來研究這種CCD結構的3D應用。

展示物件

| 圖二 : (上圖)由imec提出的氧化銦鎵鋅(IGZO)3D整合式CCD記憶體區塊,包含一顆位於垂直對齊孔洞內的整合式CCD暫存器,字元線則作為CCD閘極;(下圖)CCD暫存器的截面特寫,展示一列氧化銦鎵鋅(IGZO)的MOS電容器。 |

|

(本文作者Maarten Rosmeulen于比利時魯汶的比利時微電子研究中心(imec))